Neuromorphic Hardware

In the last 50 years, the semiconductor industry has gone through two distinct eras of scaling: the geometric (or classical) scaling era and the equivalent (or effective) scaling era. As transistor and memory features approach 10 nanometers, it is apparent that room for further scaling is running out. Additionally, the rise of data abundant computing is exacerbating the interconnect bottleneck that exists in traditional computing architecture between the compute cores and the memory blocks. High performance electronics are poised to enter a new, third era of scaling – hyper scaling. In this scaling stage, resources are added on demand to efficiently execute data abundant workloads. This era will be driven by advances in beyond-Boltzmann transistors, for logic such as negative capacitance FETs; low-power embedded non-volatile memories (NVM), like resistive and ferroelectric field effect transistor memories that will blur the boundary between logic and memory; and non-von Neumann computing paradigms, such as in-memory computing that will accelerate machine learning.

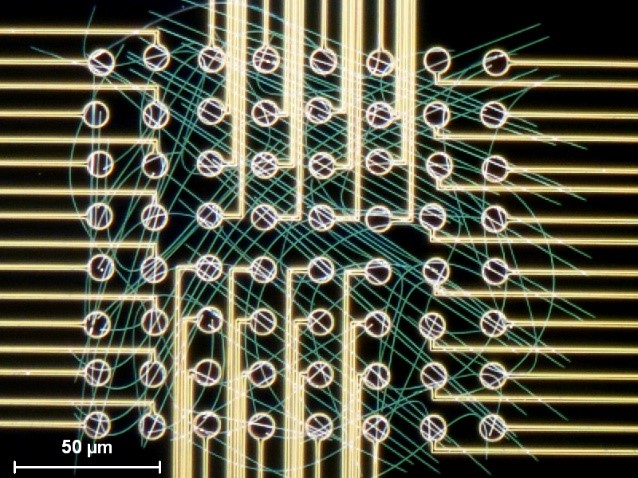

The human brain is an example of a Non-Von Neumann (Non-VN) computing paradigm for future computing systems. With an extensive parallel architecture connecting numerous low power computing elements (neurons) and adaptive memory elements (synapse), the brain outperforms modern processors. Dense arrays of non-volatile memory (NVM) elements provide an opportunity for hardware to emulate the connectivity in the human brain. Scaling dense NVM crossbar arrays to few-nanometer critical dimensions has been identified, and it has rapidly gained popularity for its possibilities in building a computing system that can simulate massive parallelism and low power operation found in the human brain.

A neuron can have as many as 10,000 inputs from other neurons, making it difficult to imitate the brain. The complex structure poses various engineering challenges such as the need for a robust computational scheme, the need for peripheral circuitry that can support massively parallel access to NVM arrays, material selection and the need to understand the impact of the inherent limitations of NVM devices.

Irradiation Effects on Non-Volatile Memory

As part of the The Interaction of Ionizing Radiation with Matter University Research Alliance (IIRM-URA), the Nino Research Group (NRG) contributes efforts to the IIRM-URA’s mission: seeking to advance the understanding of radiation-material interactions with the goal of developing and integrating technology to improve nuclear survivability and response.

NRG performs research on non-volatile memory. We develop detailed understanding of radiation effects in emerging non-volatile memory and non-traditional computing fabrics. We characterize radiation effects in ferroelectric field-effect transistor (FeFET) memory devices and their arrays to understand the basic mechanisms of ionization-induced charge generation, collection, and transport in these devices. We are using this understanding to improve FeFET radiation tolerance to total ionizing dose, high dose rate and single-event effects. We are also establishing simulation platforms for multi-scale materials, devices, and circuits to mitigate the impact of radiation exposure and improve FeFET resilience using novel electrical masking techniques.

For more details of our work in this area, please check out our publications:

Complementary resistive switching in core–shell nanowires

Resistive switching in atomic layer deposited HfO2/ZrO2 nanolayer stacks

Effect of a DC bias on the conductivity of gadolinia doped ceria thin films

hi